How Kandou has been getting ready to unlock AI from day one

There’s no bigger question facing the tech sector today than how to scale AI. Kandou’s chiplet designs are providing part of the answer, assisting the biggest memory users like hyperscalers with the jump in memory bandwidth and capacity they require. But those solutions are based on a core vision that…

There’s no bigger question facing the tech sector today than how to scale AI. Kandou’s chiplet designs are providing part of the answer, assisting the biggest memory users like hyperscalers with the jump in memory bandwidth and capacity they require.

But those solutions are based on a core vision that predates not just the AI challenge but many of the other big developments that have shaped chip design in the last ten years. Here’s how that groundwork was laid, and how unique design principles and unique manufacturing methods are now primed to unlock the next chapter in AI and Deep Learning.

In the beginning

As complicated as technology – and life – were in 2011, it was a simpler time. Kandou was founded before so many disruptive events. The pandemic was unimaginable, as was Britain’s entirely new trading relationships with Europe and the rest of the world, the war in Ukraine, and countless other changes that have shaken up global infrastructure. Siri, the first virtual assistant, was only just being launched.

Then, just as now, mathematics was the guiding principle behind the Kandou methodology. It provided the foundations of our earliest SerDes designs, and the pursuit of mathematical perfection – purer, simpler solutions to connectivity problems. It led to the development of the key ingredient in Kandou products: ChordTM Signaling.

And it’s this that has paved the way for a new era of AI scaling. So what is it?

Chord Signaling: the secret ingredient

Chip connections have historically used multiple wires – if there’s only one then throughput saturates bandwidth right away. Conceived just prior to Kandou’s launch in 2010, with what would become the company’s signature mathematical perfection, Chord Signaling provided an entirely new way of coordinating traffic across these connected wires to combat noise more effectively. Increasing the signal to noise ratio in turn increased power efficiency and transmission speed. So you can have more wires and improve pin efficiency without changing the existing differential signalling-based architecture at all. Voilà.

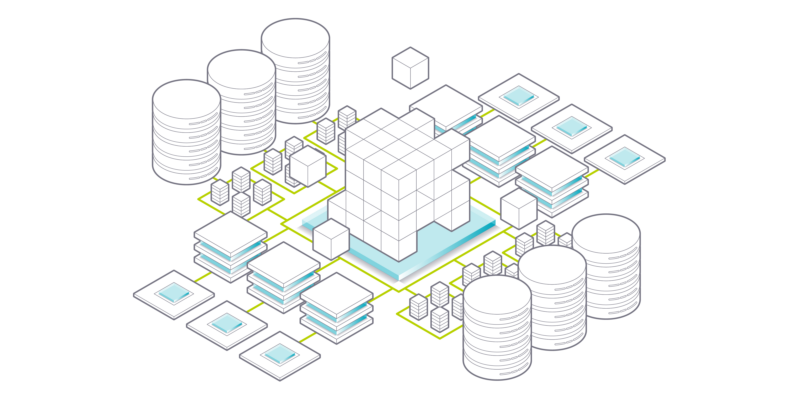

Chord Signaling made it possible to begin realising Kandou’s long-term vision for chiplets. Instead of a traditional monolithic IC, work is divided across smaller, function-specific chiplets that are then interconnected to behave as a single IC. This allows for a much more versatile and scalable approach with far simpler testing requirements. (You can read more about how chiplets came about and Kandou’s solutions in our previous blog here.) An open industry standard for an interconnect, the Universal Chiplet Interconnect ExpressTM, or UCIe, does exist but Kandou’s GlasswingTM is at present more reliable and expansive in design options.

That reliability is entirely down to Glasswing’s superior signal integrity and simple implementation. A die-to-die chiplet model has major commercial advantages, one that early adopters like Marvell Technology Group could see right away, accelerating their time to market considerably. But it also allows users to implement more complex chiplet and MCM structures. And it’s this flexibility that those working with very complex processing and memory networks in ML and AI are asking for.

Such a mathematically strong basis makes Glasswing interconnect IP extremely easy to build with – and to integrate with other technologies. So it can be configured across different vendor designs whilst still supporting needs at the highest end in terms of reach length and speed. The upshot is that the true possibilities of high efficiency, mathematically-led connections is only now revealing itself.

A very different world

Today we live in a very different world. Supply chain pressures have transformed the business landscape. A real shortage of semiconductors across certain sectors, such as automotive, is creating pressure points. The commercial edge provided by chiplets is suddenly a whole lot sharper with reliability and manufacturing methods under greater scrutiny. Everyone needs to get the absolute most out of every component.

Many expected the Universal Chiplet Interconnect Express standard to step up, but in actuality UCIe designs are thin on the ground. (Glasswing chiplet designs, on the other hand, are readily available, offering clear advantages to different sectors.)

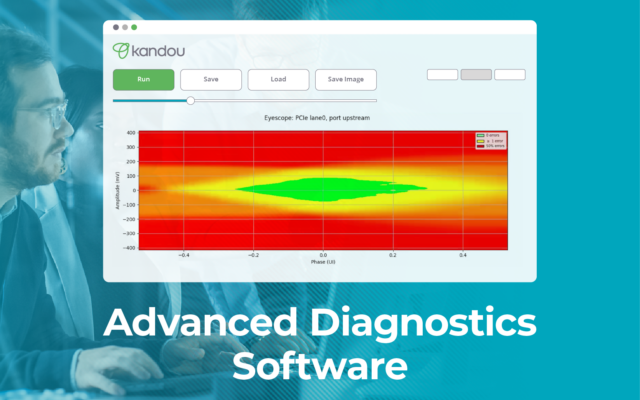

Reliability is the stand out for many – with Glasswing able to offer a far higher level of consistency and reassurance than UCIe. Forward error correction helps to guarantee the exceptionally high reliability demanded by aerospace customers, reducing the already vanishingly small error risk to basically zero.

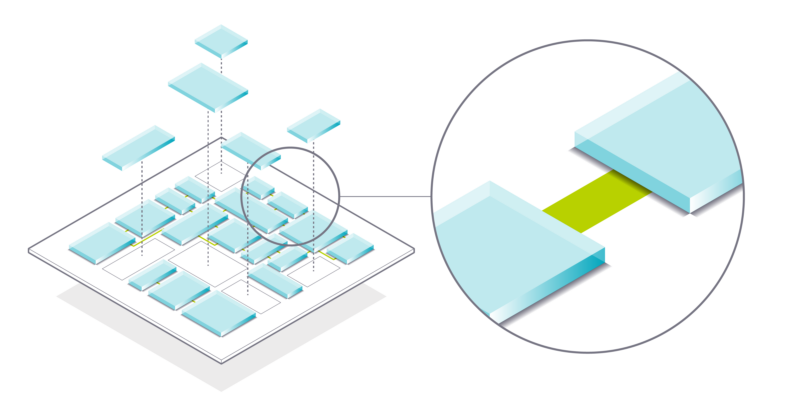

Reducing faults on the die also allows us to increase the yield for hyperscalers who need to minimise wastage. With such advanced process nodes, they can’t afford to write off 50% of chips because of faults. But a chiplet model like Glasswing, with rigorous 100% die testing, helps to minimise wastage and provide that scale.

Much of these benefits are really made possible through Kandou’s partnership with TSMC, which allows us to manufacture in ways no one else can. TSMC’s unique way of stitching chiplets together allows Kandou to collate large numbers of chiplets in one package – up to 40 in some instances.

A higher level of precision is also delivered by employing additional bleeding edge processing steps to boost signal integrity for high-speed use – micro-via connections between the layers and back-drilling plates to reduce stub size being just two. All of which give our customers an enhanced commercial edge.

But it’s the bleeding edge of AI in the next five years where Kandou’s methodology and Chord Signaling’s efficiencies are poised to allow customers to break new ground.

Unlocking AI

AI needs big thinking in order to scale. The memory wall is a major obstacle holding a lot of development and business back. How do you allow CPUs access to memory in different locations without introducing latency challenges that cancel themselves out?

84% of AI operations are inference: memory intensive speculative processes that can be opened up through Kandou’s original intuition for efficient signaling.

For instance, Chord Signaling allows Glasswing to withstand the 60mm distance required for proper DIMM signal spacing. So while some competitors are allowing 2x or 4x memory expansion, Kandou can scale memory channels up to 8x and 16x without any drop in signal integrity – a completely unique offering.

When Glasswing chiplets are paired with Kandou’s RegliTM retimer for data heavy PCIe and CXL, the potential for memory expansion at scale – both bandwidth and capacity – are huge. All without updating existing architecture, or falling foul of the latency issues that inefficient solutions like switches can’t avoid.

Kandou is jumping the memory wall and enabling the next generation of applications by starting to look at composable computing – and using mathematical precision to do it.

The answers for scaling AI are hardwired into our processes and our thinking. They always have been.